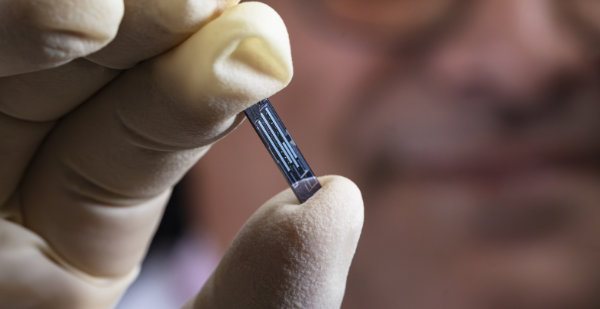

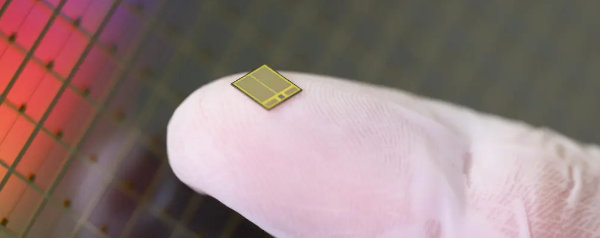

Achronixin ohjelmoitavalla eFPGA-lohkolla voidaan ohjelmoitava logiikkarakenne toteuttaa ASIC-piirillä siten, että loppukäyttäjä pystyy sovittamaan tai päivittämään ASIC-piirinsä toimintoja kenttäasennuksen jälkeenkin. Tämän tyyppinen joustavuus lisää merkittävästi ASIC-piirien sovellusaluetta tukemalla niiden päivitettävyyttä muuttuvien standardien ja algoritmien mukaisiksi.

Achronixin ohjelmoitavalla eFPGA-lohkolla voidaan ohjelmoitava logiikkarakenne toteuttaa ASIC-piirillä siten, että loppukäyttäjä pystyy sovittamaan tai päivittämään ASIC-piirinsä toimintoja kenttäasennuksen jälkeenkin. Tämän tyyppinen joustavuus lisää merkittävästi ASIC-piirien sovellusaluetta tukemalla niiden päivitettävyyttä muuttuvien standardien ja algoritmien mukaisiksi.

| Artikkelin kirjoittaja Alok Sanghavi toimii tuotemarkkinointipäällikkönä Achronix Semiconductorissa. |

Kun ASIC-piirejä suunnitellaan eFPGA-teknologialla, joudutaan käyttämään sekä ASIC- että FPGA-suunnittelutyökaluja ja tekniikoita. eFPGA-osan suunnittelu edellyttää validointia ennen suunnittelun lopullista valmistusta (tape-out), jotta voidaan varmistua, että ASIC- ja FPGA-osien suunnittelut ovat yhteensopivia ja täyttävät kaikki ajoitusvaatimukset.

Ajoitussuunnittelu on erityisen haastavaa, sillä eFPGA-rakenne voi käsittää hyvin suuren määrän erillisiä lohkoja erilaisten laitetoimintojen määrästä riippuen. Jokaisen noista suunnitteluista tulee toimia itsenäisesti jäljellä olevan ASIC-suunnittelun kanssa ja ajoitussuunnittelun voidaan todeta täsmäävän vain silloin, jos kaikki mahdolliset eFPGA-rakenteelle kohdistuvat suunnittelut täyttävät ajoitusvaatimukset.

Ilman huolellisesti mietittyä etenemisjärjestystä ajoituksen suunnittelu johtaa helposti umpikujaan. Tätä silmällä pitäen Achronix on kehittänyt metodologian, jossa kiinteästi ohjelmoitaviin ASIC-suunnittelun ominaisuuksiin yhdistyy eFPGA-suunnittelun ohjelmoitavissa olevat piirteet. Achronixin lähestymistavassa sekä staattinen ajoitusanalyysi että koko piirin ajoituksen simulointi helpottavat muutoin työlästä ja monimutkaista ajoituksen suunnittelua.

Rakenteellisena valintana eFPGA-liitännät

ASIC-suunnittelun sisällä eFPGA-rakenne voidaan toteuttaa minne tahansa, toisin sanoen yksittäiset eFPGA-portit voidaan yhdistää muihin ASIC-lohkoihin tai ulkoisten liitäntöjen puskureihin. On olemassa kaksi vaihtoehtoa yhdistää kukin eFPGA-lohkon tulo- ja lähtöliitäntä ASIC-suunnitteluun: liitännät voidaan joko rekisteröidä eFPGA-rajapintaan tai yhdistää suoraan eFPGA-rakenteeseen.

Kuva 1: Yksinkertainen ajoitusmoodi.

Kuva 2: Edistynyt ajoitusmoodi.

Kun eFPGA-rajapinnassa käytetään rekistereitä, ajoituksen suunnittelu helpottuu. ASIC-signaalit ajastetaan itsenäisesti rekisteriin ja eFPGA-signaalit ajastetaan itsenäisesti eFPGA-rakenteessa eFPGA I/O -rekisteriin. Tämän lähestymistavan seurauksena rekisteri lisää latenssikellojakson signaaleihin.

Ohittamalla eFPGA I/O -rekisterit eFPGA-liitännässä eliminoidaan ylimääräinen viivejakso. Ajoituksen suunnittelu kuitenkin vaikeutuu, sillä liitäntäpisteiden välinen signaalin ajoitusviive (timing arc) jakautuu sekä ASIC- että eFPGA-osan kesken. Tuloksena on että ASIC- ja eFPGA-osia ei voida ajastaa toisistaan riippumattomasti.

Tämän arkkitehtuurisen valinnan seurauksena kunkin signaalitien ajoituksen suunnittelussa voidaan soveltaa kahta lähestymistapaa, joita Achronix kutsuu yksinkertaiseksi ja edistyneeksi ajoitusmoodiksi. Kun käytetään I/O-rekisteriä, kyseessä on yksinkertainen ajoitusmoodi; kun rekisteri ohitetaan, kyseessä on edistynyt ajoitusmoodi. Yksinkertaisessa ajoitusmoodissa ASIC-työkaluilla tehdään ajoituksen suunnittelu ASIC-osassa ja ACE-työkaluilla eFPGA-osassa.

Edistyneessä ajoitusmoodissa on käytössä sekä ASIC- että eFPGA-työkalut. Achronixin toimittamat ohjelmakoodit ja apuvälineet automatisoivat tehtäviä, joita tarvitaan molempien työkalujen yhteensovittamisessa sekä ASIC- että eFPGA-osien ajoituksen suunnittelua varten. Seuraavassa keskitytään edistyneeseen ajoitusmoodiin, jossa strukturoimaton lähestymistapa voi aiheuttaa ongelmia.

Edistyneen ajoitusmoodin toteutussekvenssi

Sen sijaan että yksittäinen suunnittelija toteuttaisi sekä ASIC- että eFPGA-osien suunnittelun, on paljon todennäköisempää, että näiden osien suunnitteluun osallistuu useita suunnittelijoita tai tiimejä. Itse asiassa koko eFPGA-osan integrointiprosessi ASIC-osan kanssa pitää sisällään erilaisia rooleja erityisesti back-end-suunnittelua tekevän tiimin osalta, ja edistyneen ajoitussuunnittelun vaiheet voidaankin esittää kuvan 3 vuokaaviolla:

Kuva 3: Ajoituksen suunnittelu edistyneessä moodissa

Ensin back-end-suunnittelutiimi suorittaa staattisen ajoitusanalyysin (STA) koko suunnittelun osalta valittuja STA-työkaluja käyttäen.Tämän analyysin aikana käytetään valitun puolijohdetoimittajan ASIC.lib-tiedostoa. Erilliset ajot suoritetaan kullekin halutulle kellotusskenaariolle, jossa tavoitetaajuus on asetettu mahdollisimman haasteelliseksi.

Seuraavaksi tiimi määrittää Achronixin ohjelmistokoodia käyttäen ASIC- ja eFPGA-osat kustakin eFPGA-osaan tulevasta tai lähtevästä signaalista. Saatujen viiveiden perusteella määritetään rajoitteet ACE-työkaluille. Ilman näiden viiveiden hyödyntämistä ACE-työkalulla ei ole näkyvyyttä eFPGA-lohkon ulkopuolella olevaan ajoitukseen. Kyseisten viiveiden ansiosta ACE-työkalulla saadaan siis näkemys ajastuksesta eFPGA-lohkon ulkopuolelta käsin. Näin ollen ACE-työkalulla voidaan varmistaa oikea ajoitus. Jos ajoitus läpäisee jokaisen suunnittelun, on prosessi loppuun suoritettu. Jos ajoitus ei läpäise koko suunnittelua, yksi vaihtoehto on poistaa joitakin kombinaatiologiikan lohkoja viallisilta signaaliteiltä, ja käynnistää uudelleen vaiheesta yksi. Toinen vaihtoehto on palata vaiheeseen yksi ja joko nostaa tavoitetaajuutta entisestään tai lisätä jonkin verran vioittuneiden signaalien marginaalia.

ASIC- ja eFPGA-osien tehokas ajoituksen suunnittelu

Achronixin ajoitussuunnittelun metodologia tarjoaa suoraviivaisen tavan ajastaa sekä Speedcore sirun eFPGA- että ASIC-osat. Metodologia käyttää hyväksi sekä standardeja ASIC- että ACE-työkaluja. Prosessi mahdollistaa sekä staattisen ajoitusanalyysin että koko sirun ajastuksen simuloinnin. Ajastus voidaan varmistaa prosessin ja toimintapisteiden yli eri toimintatiloissa ja jopa monille eri suunnitteluille, jotka sijaitsevat eFPGA-osassa. Suunnittelutiimit voivat luottaa saatuihin tuloksiin heti, kun työkalut ilmaisevat, että ajoitusvaatimukset on saavutettu.

Tämä artikkeli on yhteenveto samaa aihetta käsittelevästä dokumentista.

Lisäksi eFPGA:n käyttö SoC-piireissä muuttaa loppukäyttäjän, suunnittelutiimin ja puolijohdetoimittajan välistä toimintamallia, mistä lisätietoa on luettavissa Achronixin blogissa: Who’s Who in the Zoo.

– Haluamme olla tekoälyn hyödyntämisen edelläkävijöitä, ja se vaatii luottamuksen rakentamista asiakkaiden suuntaan. Pelkkä yrityksen oma lupaus ei enää riitä, sanoo Julius Manni. Vincit on saanut ensimmäisenä Suomessa akkreditoidun ISO/IEC 42001 -sertifikaatin.

– Haluamme olla tekoälyn hyödyntämisen edelläkävijöitä, ja se vaatii luottamuksen rakentamista asiakkaiden suuntaan. Pelkkä yrityksen oma lupaus ei enää riitä, sanoo Julius Manni. Vincit on saanut ensimmäisenä Suomessa akkreditoidun ISO/IEC 42001 -sertifikaatin.